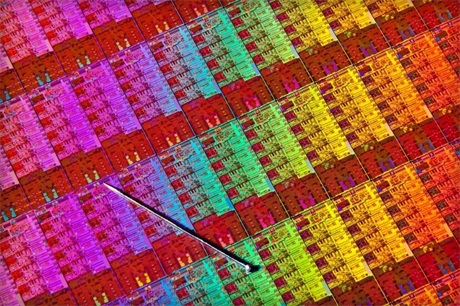

������������Ħ�������Ƿ������ڵ����оƬ����ҵ��ר����Ҳ�Ǹ������ԡ�����������Ƽ���Ĺ���Ҫ����ʱ��ʧЧ�ˣ����������ɻ�֮ʱ���������õļ��㼼����ͻȻ������һ������Ϣ����������˹����������ʵ���ҵ�һ���ŶӴ������������ޣ���������Ƴ̴�14nm��С����1nm��

�ڼ��ɵ�·�����У������ߴ����ʶ��ָ�뵼�������е���С�ߴ硣����CMOS�����У������ߴ�ĵ��ʹ���Ϊ��դ���Ŀ��ȣ�Ҳ����MOS�����Ĺ������ȡ�һ��������̸��CPU�ĸ��»�����ʱ��Ҳ�ὲ�����ƵĻ��������ߴ�ԽС��оƬ�ļ��ɶȾ�Խ�ߣ�����Խǿ��������ȴԽ�͡�

�������칤����ʲô��˼

��ν�Ķ���nmָ����CPU���γɵĻ�������������뵼�峡ЧӦ�����դ���Ŀ��ȣ����դ����դ��Խ�̣���������ͬ�ߴ�Ĺ�Ƭ���ܼ��ɸ���ľ���ܣ�Intel�������ƽ�դ����130nm��С��90nmʱ�����Ӧ�ľ������ռ�õ����Ҳ��֮��С��һ�룻ͬ������оƬ�ľ���ܼ��ɶȴ����൱������£�ʹ�ø��Ƚ������칤�գ������ľ���оƬ������Ļ�ԽС�����ɱ�Ҳ��Խ�͡�

�������������1nm�����ж�С���������ͷ�����������ߵĿ��Ƚ�ΪԼ5�����ס��������С��Ҳ�ܺõ�������δ���ᱡ��������

ͻ��������������

�Ƴ̣��������������Ƶ���С�����羧����С��20�������ң��������������Ȼ��������ʱ�ĵ羧�����©�����������С���ʱ��õ�Ч�档

��Ϊ������������ն���϶��ɣ�һ��Դ����һ��©����һ���ż���������Դ������©������ʱ�������ż������ƣ�ͨ�������ͶϿ�����ʩ�ӵĵ�ѹ������Ӧ����ʱ���ӽ�ʧȥ���ơ�Ϊ�˸���������⣬�ڴ�ͳ�Ĺ����У���˵�Ӵ���ֻ��һ�������Dz�����FinFET��Tri-Gate�������Ӵ������ĸ��ӵ����壬�ܹ��������ӽӴ��������ʹSource-Drain�˱�ø�С������С�ߴ��кܴ�İ�����Ҳ�ܺõļ��������������µ�©������

���еľ��������

����ܵ��Ƴ̴�Сһֱ��Ӱ����㼼����������Ҫ���ء��ڼ��ɵ�·�����У������ԽС����ͬ�������оƬ�ϼ��ɵ�Խ�࣬�����Ľ�����Ǵ����������ܺ��ĵõ���Ľ�����

��ĿǰоƬ�����칤��������7nm�Ѿ����������ޣ�һ�㵱����ܵĴ�С����7nm������������̬�ϻ�dz��ļ��У��Ӷ�������������ЧӦ�����оƬ���칤�մ����˾����ս������Ҫͻ�����ŵ�·��ơ�

��ǰ������оƬ��ͷ��ʾ���ǽ�Ѱ����������ԭ��������7nm����ܣ���������˹����������ʵ�����Ѿ�������ǰ�档�ɹ����Ƴ�����1���ף�������������̼��������⣨MoS 2���Ȳ��ϵ����ã���������������ܺ�����Ħ�����ɵĹؼ����ϣ�Ҳ�Ǵ˴��о��ɹ��Ĺؼ�Ҫ�ء�

�����������о��Դ��ڳ����Σ��Ͼ�����оƬ�г�����14nm�Ƴ�ͳ���ţ�����14nm��оƬ�Ͼ��ѳ�����10�ڶ������ܣ�Ҫ�뽫�������С��1nm�����ģ�����Ļ������ѻ��DZȽϴ�ġ��ܶ���֮�������о����зdz���Ҫ��ָ�����壬���²��ϵķ��֣�����δ���������ش��������������������������������Ҳ��Ħ�����ɼ������Ĵ���Ԥ�ԡ�

������

�ڿƼ���������ӵ���Ѷ�У�Ϊ����˿���룻�ڿƼ�ý��ټ������Ĺ۵������������죻���Ź�һ˿ϸ�ڣ���������һ���뷨��������Ŭ��Ϊ���ṩ���õ���Ѷ���۵㡢��Դ��

�����ɹ��ں�����ͬ�����ͽ���ͷ�� �Ѻ� ��Ѷ�챨 ���� ��˵����ſͻ���

��վ��www.zhiwp.com

��������ţ�dc_289466629

������ϵ�绰��0755-32949447

)

)

����˵�������а�