�����չ��������£�����·����ǣ������ߡ��Զ������ܰѹ������ԾͰ����ӷ��ˡ����ָİ塢���ֲ��ȶ������ֵ��ԡ����ַ��ߡ������������������ź������ԡ�

����

�������Ǻ���Ľ�������������ӵĵ�·������ʵ����֪�����˵ĵ�·Ϊʲô���ӣ�����֪��PCB��Ƶ�ʱ��ע����Щ�ؼ���ע��㡣ƾ���Լ���ϲ�úо����е�·��ơ�

�����ܸ�Ц��һ�����飺��ʱ�չ���������һ�������곤�Ĺ���ʦ��Ϊʲô���˵ĵ�·���������������ߣ�

������Ҳ�Ǻ��±ƵĻش��ң���֪������������Ϊ�˷�ֹ�źŷ����ȥ���������źš�������Ϊ���Ǹ��ٵ��źţ���������Խ��Խ�����䡣���������������Ȼ�Ǵ���ģ�

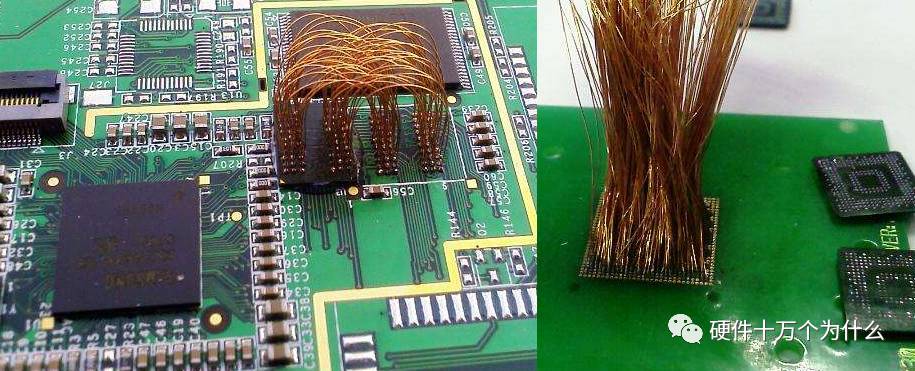

�������ǣ������˸�Ц������һ��FPGA�ĵ�·������������ߵ��źţ�ʱ�ӣ������������ߡ�

���������ҵ������ڻ��������ʱ�����ҵĸ��������뿪�˵�һ�ݹ�����ȥ�ˡ���Ϊ���������ҵ�Ӳ�����룺Ҫ��������Ӳ���������ӵ�Ӳ�������ɿ��Ե�Ӳ��������ֵǮ��Ӳ����

�������˻�Ϊ֮���൱��ġ��ź������ԡ�����ѵ���ҿ�ʼ��Ƹ������ʵĵ�·���Դ��߽��˸��ٵ�·��Ϊ�Ҵ���һ���µ����磬�����������ٵ�·������������ʹPCB���߳��ȡ����ȡ�λ�ü�ʹ������Ҳ���ᱩ¶ʲô����ĵ�·���ź���������Ϊ��Ҫ��һ�Ż������������ϵ��ź������ԣ��ɷ�ָ����Դ��������ԴԪ������������źŵ�ѹ�͵������쳣�����������ϵ��������ţ��ź�ʱ���Լ��ź�ʱ���ϵĶ������λ��ѧϰ�á��ź������ԡ�������ָ��������ȷ�����ԭ��ͼ��PCB�dz���Ҫ�������ܼ�Ԧ���ź�Ƶ��Խ�ߡ��ź�����Խ�죬Ӳ������ʦ��ԽֵǮ��

�����ڻ�Ϊ����ְ�ʸ�����Ӳ��������������Դ�ڰٶȣ�

�����ر�֪ʶ |

����1�� |

����2�� |

����3�� |

����4�� |

����5�� |

����6�� |

|

������������֪ʶ |

������Ԫ���Լ��� |

�� |

|||||

����Ԫ�������� |

�� |

||||||

����CAD��ƽӿ�֪ʶ |

�� |

||||||

�������ɱ������Ӧ�� |

�� |

||||||

����������ƻ��� |

�� |

||||||

��������Ӧ����ɿ��� |

�� |

||||||

�����ź������Է��� |

�� |

||||||

���������Դ��� |

�� |

||||||

����ͨ�ô��������� |

�� |

||||||

����ʱ�Ӽ������� |

�� |

||||||

����ר���֪ʶ |

����EMC��� |

�� |

|||||

����������� |

�� |

||||||

��������� |

�� |

||||||

�����ɲ�������� |

�� |

||||||

��������������� |

�� |

||||||

�����ɿ��Թ������ |

�� |

||||||

�����ɰ�װ����� |

�� |

||||||

������������� |

�� |

������Ȼ��ô��Ҫ�Ŀ�Ŀ�����о���ϸ�¡�רҵ������Ҳ�Ƿdz���Ҫ���ۺ�Ͷ��ġ�Ӳʮ���ε����»��Я�ּ�λ�ڸ���������ơ��ź������Է���dz������ר��Ϊ�����һ�����ź������ԡ�����Ļ��

1.�������ź������Թ��ںŴ�ʼ�˺Ͳ���

����֪���������ںš��ź������ԡ����ںŴ�ʼ�˺Ͳ�����

���������鼮����Դ�����ԡ������ߣ�

�����鼮�����ٵ�·����ʵս�������ߡ�

����2.����

����17������Ӳ������ʦ��2000���ҵ���Ͼ�������ѧ�Զ�����ϵ��˶ʿ����

��������ְ����ͨѶ�Ͼ��о�����Ӳ������ʦ����������ͨѶӲ��������

�����dz��ḻ��ʱ������ֵ�·��ز������ۼ�ʵս���顣

����3.���

����ʮ���꼯�ɵ�·���������Ծ��飻

�����ǵ¿Ƽ��������Ƽ�������AE��

����רע�ڸ������ֵ�·������뵼����ԣ�

���������ź������Բ�������̵����⡣

����4.��������Ӳ��ʮ���Ϊʲô��ʼ�ˣ�У����

����Ӳ��ʮ���Ϊʲô��ʼ�ˣ�6��+����ʦ��ע��

����ʮ����������Ӳ������ʦ��

����2008~2015�껪Ϊ��������˾���ḻ�ķ������������飬���ź����豸Ƕ��ʽ�������������麭�ǣ�FPGA��X86��PPC�����DSP��MIPS�����ARM�����ָ�������ϵͳ��

����ӵ�������й�ר������������ר����

������Ϊ2012���Ƹ��ˣ�����˼�뵼ʦ��

�����������⣺

�����ź�������֮ʱ����ơ���������

�������ٴ��нӿ����߲�����һ���Բ���������������

������Դ������ǰ�ؼ����������

�������ٵ�·������������ա�������

�����������α� + ����ɵĸ��ٵ�·��֪ʶ����+ ������Ʒ����

����Ӳʮ�ں��ݵļ�������ֳ��𱬣������ڵĹۿ�ֱ����ͬѧ��ʾ������ô�õļ���������������ڣ��ⲻ��ѧ����

�������ڣ�Ӳʮ���ˣ�

����ʱ��ص㣺

����ʱ�䣺2017-07-08 ����09:30~15:30

�����ص㣺�㶫���ڸ�������ǿ�����ʴ�������

����

����

�����ֳ��齱��

�����ֳ���ͨ���齱�ķ�ʽ�ͳ�����100�ݾ�����Ʒ��

����

�����ź�����������鼮�����ü������ͷ����籦��������Ʒ��

��������������

�����Ӻ��ѣ�ת��������Ϣ������Ȧ����ͼ�����᳡������Ա��Ӳʮ������������������롶����_Ӳ��ʮ���Ϊʲô����������Ⱥ����ȡ�������ӣ����ܵ��ֳ������ѽ�Ⱥ���ֱ�����ӡ�

)

)

����˵�������а�